I.MẠCH GIẢI MÃ

Mạch giải mã là mạch có chức năng ngược lại với mạch mã hoá tức là nếu có 1 mã số áp vào ngõ vào thì tương ứng sẽ có 1 ngõ ra được tác động, mã ngõ vào thường ít hơn mã ngõ ra. Tất nhiên ngõ vào cho phép phải được bật lên cho chức năng giải mã. Mạch giải mã được ứng dụng chính trong ghép kênh dữ liệu, hiển thị led 7 đoạn, giải mã địa chỉ bộ nhớ. Hình dưới là sơ đồ khối của mạch giải mã

1.Giải mã 3 sang 8

Mạch giải mã 3 đường sang 8 đường bao gồm 3 ngõ vào tạo nên 8 tổ hợp trạng thái, ứng với mỗi tổ hợp trạng thái được áp vào sẽ có 1 ngõ ra được tác động.

Bạn đang xem: Mạch Giải Mã Âm Thanh Sku5571

Hình 2.1.6 Khối giải mã 3 sang 8 |

Bảng sự thật mạch giải mã 3 sang 8 |

Từ bảng sự thật ta có thể vẽ được sơ đồ mạch logic của mạch giải mã trên

Hình 2.1.7 Cấu trúc mạch giải mã 3 sang 8

Rút gọn hàm logic sử dụng mạch giải mã :

Nhiều hàm logic có ngõ ra là tổ hợp của nhiều ngõ vào có thể được xây dựng từ mạch giải mã kết hợp với một số cổng logic ở ngõ ra(mạch giải mã chính là 1 mạch tổ hợp nhiều cổng logic cỡ MSI). Mạch giải mã đặc biệt hiệu quả hơn so với việc sử dụng các cổng logic rời trong trường hợp có nhiều tổ hợp ngõ ra.

Ví dụ sau thực hiện mạch cộng 3 số X, Y, Z cho tổng là S và số nhớ là C thực hiện bằng mạch giải mã :

Giả sử mạch cộng thực hiện chức năng logic như bảng sau :

| X | Y | Z | S | C |

| 0

0 0 0 1 1 1 1 |

0

0 1 1 0 0 1 1 |

0

1 0 1 0 1 0 1 |

0

1 1 0 1 0 1 1 |

0

0 0 1 0 1 1 1 |

Từ bảng cho phép ta xác định được các tổ hợp logic ngõ vào để S rồi C ở mức cao

| S(x, y, z) = (1,2,4,7) |

| C(x, y, z) = (3,5,6,7) |

Như vậy sẽ cần 1 cổng OR để nối chung các tổ hợp logic thứ 1, 2, 4, 7 để đưa ra ngõ S

Tương tự ngõ ra C cũng cần 1 cổng OR với ngõ vào là tổ hợp logic thứ 2, 5, 6, 7

Vậy mạch giải mã thực hiện bảng logic trên sẽ được mắc như sau :

Hình 2.1.11 Ứng dụng mạch giải mã làm mạch cộng

2.Mạch giải mã BCD sang thập phân

Hình 2.1.3 diễn tả cho hoạt động của mạch mã hoá nếu phím 2 được nhấn, đường A2 sẽ có mức cao, mã số ra là 0010. Bây giờ ta có mã số áp ngõ vào giải mã là 0010 thì ngõ ra thứ 2 tương ứng sẽ được tác động (giả sử nối tới 1 đèn led thì sẽ làm nó sáng).

74LS42 là IC làm nhiệm vụ giải mã 4 đường sang 10 đường. Cấu tạo logic và bảng hoạt động của nó sẽ minh hoạ rõ hơn cho mạch giải mã này :

Hình 2.1.8 Kí hiệu khối của 74LS42

Hình 2.1.9 Cấu trúc mạch của 74LS42, giải mã 4 sang 10

Bảng sự thật của 74LS42

Để ý là vì có 4 ngõ vào nên sẽ có 16 trạng thái logic ngõ ra. Ở đây chỉ sử dụng 10 trạng thái logic đầu, 6 trạng thái sau không dùng. Với mạch giải mã 4 sang 16 thì sẽ tận dụng hết số trạng thái ra. Một điểm nữa là các ngõ ra của 7442 tác động ở mức thấp

Về nguyên tắc ta có thể mã hoá từ n đường sang m đường và ngược lại giải mã từ m đường sang n đường, chức năng giữa mã hoá và giải mã không rõ rệt lắm, chúng đều làm nhiệm vụ chuyển đổi từ mã này sang mã khác (những mạch ở trên đều nói đến mã hệ 2, thực ra còn nhiều loại mã khác). Cũng chỉ có một số chúng được tích hợp sẵn trong IC như 7441, 7442 là giải mã BCD sang thập phân, 7443 là giải mã thừa 3 sang thập phân, …

Nhiều mạch giải mã còn có thêm mạch chịu dòng hay thế cao hơn mạch logic TTL thông thường nên còn gọi là mạch giải mã thúc

Mạch sau minh hoạ cách kết hợp mạch đếm sẽ học ở chương sau với mạch giải mã để cung cấp các hoạt động định thời và định thứ tự, IC giải mã thúc 7445 được dùng vì tải là động cơ có áp lớn dòng lớn ngoài sức cung cấp của các IC giải mã thường

Hình 2.1.10 Ứng dụng 74LS45

Hình trên cho thấy, mạch đếm tạo ra 16 tổ hợp trạng thái cho mạch mã hoá. Phải 4 chu kì xung ck thì Q3 mới xuống thấp, cho phép động cơ được cấp nguồn; còn đèn được mở chỉ sau 8 chu kì xung ck. Thời gian mở của tải là 1 chu kì xung ck. Ta có thể điều chỉnh thời gian này từ mạch dao động tạo xung ck. Về nguyên tắc hoạt động của mạch đếm 74LS90 ta sẽ tìm hiểu ở chương sau.

3.Giải mã BCD sang led 7 đoạn

Một dạng mạch giải mã khác rất hay sử dụng trong hiển thị led 7 đoạn đó là mạch giải mã BCD sang led 7 đoạn. Mạch này phức tạp hơn nhiều so với mạch giải mã BCD sang thập phân đã nói ở phần trước bởi vì mạch khi này phải cho ra tổ hợp có nhiều ngõ ra lên cao xuống thấp hơn (tuỳ loại đèn led anode chung hay cathode chung) để làm các đoạn led cần thiết sáng tạo nên các số hay kí tự.

Led 7 đoạn

Trước hết hãy xem qua cấu trúc và loại đèn led 7 đoạn của một số đèn được cấu tạo bởi 7 đoạn led có chung anode (AC) hay cathode (KC); được sắp xếp hình số 8 vuông (như hình trên) ngoài ra còn có 1 led con được đặt làm dấu phẩy thập phân cho số hiện thị; nó được điều khiển riêng biệt không qua mạch giải mã. Các chân ra của led được sắp xếp thành 2 hàng chân ở giữa mỗi hàng chân là A chung hay K chung. Thứ tự sắp xếp cho 2 loại như trình bày ở dưới đây.

Hình 2.1.12 Cấu trúc và chân ra của 1 dạng led 7 đoạn

Hình 2.1.13 Led 7 đoạn loại anode chung và cathod chung cùng với mạch thúc giải mã

Để đèn led hiển thị 1 số nào thì các thanh led tương ứng phải sáng lên, do đó, các thanh led đều phải được phân cực bởi các điện trở khoảng 180 đến 390 ohm với nguồn cấp chuẩn thường là 5V. IC giải mã sẽ có nhiệm vụ nối các chân a, b,.. g của led xuống mass hay lên nguồn (tuỳ A chung hay K chung)

Khảo sát 74LS47

Với mạch giải mã ở trên ta có thể dùng 74LS47. Đây là IC giải mã đồng thời thúc trực tiếp led 7 đoạn loại Anode chung luôn vì nó có các ngõ ra cực thu để hở và khả năng nhận dòng đủ lớn. Sơ đồ chân của IC như sau :

Hình 2.1.15 Kí hiệu khối và chân ra 74LS47

Trong đó

A, B, C, D là các ngõ vào mã BCDRBI là ngõ vào xoá dợn sóng

LT là ngõ thử đèn

BI/RBO là ngõ vào xoá hay ngõ ra xoá rợna tới g là các ngõ ra (cực thu để hở)

Hình 2.1.16 Cấu trúc bên trong của 74LS47 và dạng số hiển thị

Hoạt động của IC được tóm tắt theo bảng dưới đây Nhận thấy các ngõ ra mạch giải mã tác động ở mức thấp (0) thì led tương ứng sáng

Ngoài 10 số từ 0 đến 9 được giải mã, mạch cũng còn giải mã được 6 trạng thái khác, ở đây không dùng đến (ghi chú 2)Để hoạt động giải mã xảy ra bình thường thì chân LT và BI/RBO phải ở mức cao

Muốn thử đèn led để các led đều sáng hết thì kéo chân LT xuống thấp (ghi chú 5)Muốn xoá các số (tắt hết led) thì kéo chân BI xuống thấp (ghi chú 3)

Khi cần giải mã nhiều led 7 đoạn ta cũng có thể ghép nhiều tầng IC, muốn xoá số 0 vô nghĩa ở trước thì nối chân RBI của tầng đầu xuống thấp, khi này chân ra RBO cũng xuống thấp và được nối tới tầng sau nếu muốn xoá tiếp số 0 vô nghĩa của tầng đó (ghi chú 4). Riêng tầng cuối cũng thì RBI để trống hay để mức cao để vẫn hiển thị số 0 cuối cùng

Ví dụ : Hãy xem một ứng dụng của mạch giải mã led 7 đoạn :

Hình 2.1.14 Ứng dụng mạch giải mã 74LS47

Mạch dao động tạo ra xung kích cho mạch đếm, ta có thể điều chỉnh chu kì xung để mạch đếm nhanh hay chậm

Mạch đếm tạo ra mã số đếm BCD một cách tự động đưa tới mạch giải mã có thể là cho đếm lên hay đếm xuống

Mạch giải mã sẽ giải mã BCD sang led 7 đoạn để hiển thị số đếm thập phân

Bây giờ ta có thể thay mạch dao động bằng 1 bộ cảm biến chẳng hạn dùng bộ thu phát led đặt ở cửa vào nếu mỗi lần có 1 người vào thì bộ cảm biến sẽ tạo 1 xung kích kích cho mạch đếm. Lưu ý rằng IC 7490 là IC đếm chia 10 không đồng bộ mà ta sẽ học ở chương sau

Như vậy với ứng dụng này ta đã có hệ thống đếm số người vào cổng cũng có thể đếm sản phẩm qua băng truyền,… tất nhiên chỉ hạn chế ở số người vào nhiều nhất là 9.

Khi này hình trên được trình bày ở dạng mạch cụ thể như sau :

Hình 2.1.17 Minh hoạ ứng dụng 74LS47 trong mạch hiển thị led 7 đoạn

Những IC giải mã thúc led 7 đoạn khác

Ngoài 74LS47 ra còn có một số IC cũng làm chức năng giải mã thúc led 7 đoạn được kể ra ở đây :

Một số IC còn có khả năng tổng hợp mạch đếm, chốt và giả mã thúc trong cùng 1 vỏ như 74142, 74143, 74144 thậm chỉ bao gồm cả led trong đó như HP5082, TIL308.

IC giải mã thúc loại CMOS

Họ CMOS cũng có các IC giải mã thúc led 7 đoạn tương ứng, ở đây giới thiệu qua về 4511

4511 có khả năng thúc, giải mã và chốt dữ liệu cùng 1 lúc. Các ngõ ra như đã thấy ở trên đều tác động mức cao nên 4511 dùng cho giải mã led 7 đoạn loại K chung. Các chân BI, LT cũng có chức năng tương tự như bên 74LS47. Đặc biệt chân LE cho phép chốt dữ liệu lại khi nó ở cao. Vì cấu trúc có sẵn mạch thúc 8421 trong nó nên 4511 còn có thể thức trực tiếp thúc hay thúc được tải lớn hơn như đèn khí nóng sáng, tinh thể lỏng, huỳnh quang chân không

Hình 2.1.18 Kí hiệu khối và chân ra của 4511

Những ứng dụng chính của nó là mạch thúc hiển thị trong các bộ đếm, đồng hồ DVM…, thúc hiển thị tính toán máy tính, thúc giải mã trong các bộ định thời, đồng hồ khác nhau

Bảng hoạt động của 4511 như dưới đây, chi tiết về nó bạn có thể xem trong phần datasheet.

Mạch giải mã hay decoder là một mạch tổ hợp có ‘n’ dòng đầu vào và tối đa 2n dòng đầu ra. Một trong các đầu ra này sẽ hoạt động ở mức cao dựa trên sự kết hợp của các đầu vào hiện có, khi mạch giải mã được bật. Điều đó có nghĩa là mạch giải mã phát hiện một mã cụ thể. Đầu ra của mạch giải mã là các số hạng tối thiểu của dòng biến đầu vào ‘n’, khi nó được kích hoạt.

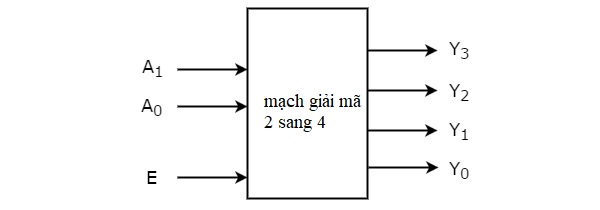

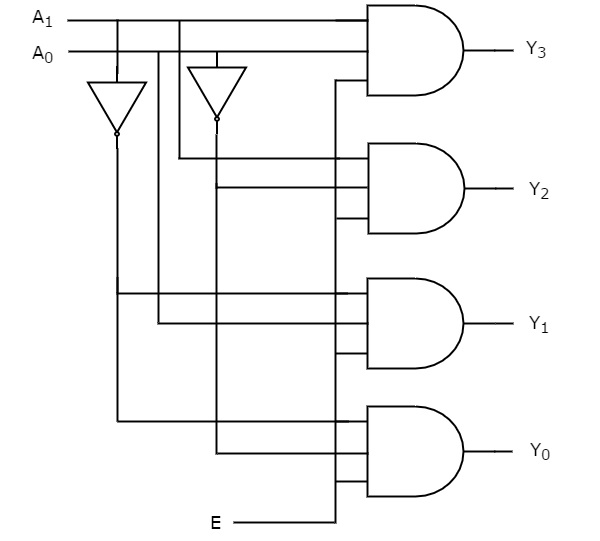

Mạch giải mã 2 sang 4

Cho mạch giải mã 2 sang 4 có hai đầu vào A1 & A0 và bốn đầu ra Y3, Y2, Y1 & Y0. Sơ đồ khối của mạch giải mã 2 sang 4 được thể hiện trong hình sau.

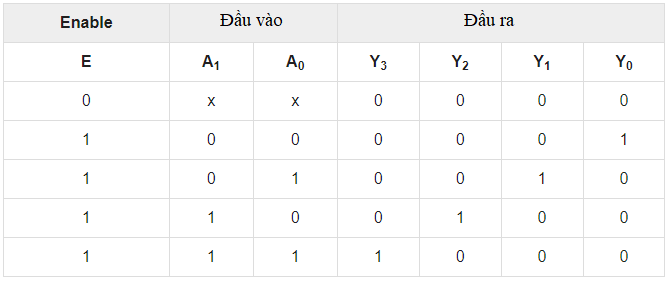

Một trong bốn đầu ra này sẽ là ‘1’ cho mỗi tổ hợp đầu vào khi bật, E là ‘1’. Bảng chân trị của mạch giải mã 2 sang 4 như bên dưới.

Từ bảng chân trị, chúng ta có thể viết các hàm Boolean cho mỗi đầu ra như sau:

Y3 = E.A1.A0

Y2 = E.A1.A0 ′

Y1 = E.A1′.A0

Y0 = E.A1′.A0 ′

Mỗi đầu ra có một số hạng tích (product term). Vì vậy, có tổng cộng bốn số hạng tích. Chúng tôi có thể triển khai bốn số hạng tích này bằng cách sử dụng bốn cổng AND có ba đầu vào mỗi đầu vào & hai inverter. Sơ đồ mạch giải mã 2 sang 4 như trong hình sau.

Do đó, các đầu ra của mạch giải mã 2 sang 4 là số hạng tối thiểu của hai biến đầu vào A1 & A0, khi kích hoạt, E bằng một. Nếu kích hoạt, E bằng 0, thì tất cả các đầu ra của mạch giải mã sẽ bằng không.

Tương tự, mạch giải mã 3 sang 8 tạo ra tám số hạng tối thiểu của ba biến đầu vào A2, A1 & A0 và mạch giải mã 4 sang 16 tạo ra mười sáu số hạng tối thiểu của bốn biến đầu vào A3, A2, A1 & A0.

Triển khai mạch giải mã bậc cao hơn

Bây giờ, chúng ta hãy triển khai hai mạch giải mã bậc cao sau đây bằng cách sử dụng mạch giải mã bậc thấp hơn.

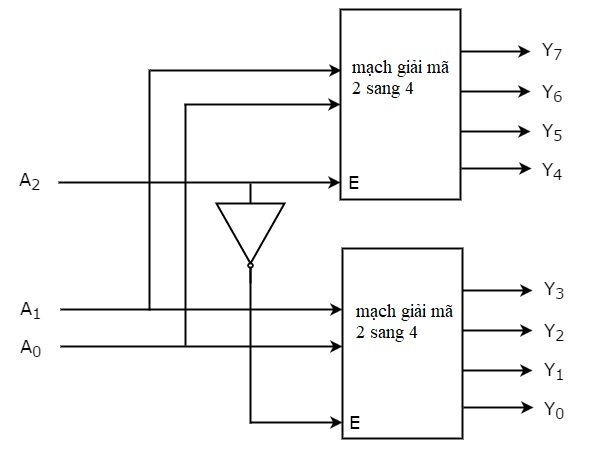

Mạch giải mã 3 sang 8

Mạch giải mã 4 sang 16

Mạch giải mã 3 sang 8

Trong phần này, chúng ta hãy triển khai mạch giải mã 3 sang 8 bằng cách sử dụng mạch giải mã 2 sang 4. Chúng ta biết rằng mạch giải mã 2 sang 4 có hai đầu vào, A1 & A0 và bốn đầu ra, Y3 đến Y0. Trong khi, mạch giải mã 3 sang 8 có ba đầu vào A2, A1 & A0 và tám đầu ra, Y7 đến Y0.

Chúng ta có thể tìm số lượng mạch giải mã bậc thấp hơn cần thiết để triển khai mạch giải mã bậc cao hơn bằng cách sử dụng công thức sau.

Số lượng bộ giải mã bậc thấp hơn cần thiết = m2/m1

Trong đó

m1 là số đầu ra của bộ giải mã bậc dưới.

m2 là số đầu ra của bộ giải mã bậc cao hơn.

Ở đây, m1 = 4 và m2 = 8. Thay thế, hai giá trị này trong công thức trên ta có

m2/m1 = 2

Do đó, chúng ta cần 2 mạch giải mã 2 sang 4 để triển khai một mạch giải mã 3 sang 8. Sơ đồ khối của mạch giải mã 3 sang 8 sử dụng mạch giải mã 2 sang 4 được thể hiện trong hình sau.

Các đầu vào song song A1 & A0 được áp dụng cho mỗi mạch giả mã 2 sang 4. Phần bổ sung của đầu vào A2 được kết nối với Enable, E của bộ giải mã thấp hơn từ 2 sang 4 để nhận các đầu ra, Y3 đến Y0. Đây là bốn số hạng tối thiểu thấp hơn. Đầu vào, A2 được kết nối trực tiếp với Enable, E của bộ giải mã trên 2 sang 4 để nhận các đầu ra, Y7 đến Y4. Đây là bốn số hạng tối thiểu cao hơn.

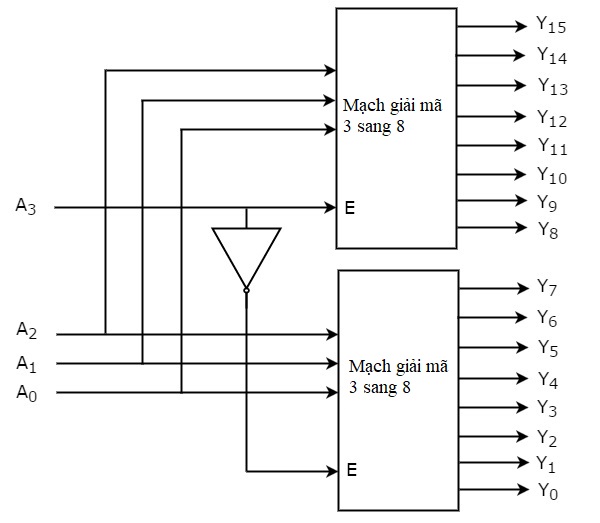

Mạch giải mã 4 sang 16

Trong phần này, chúng ta hãy triển khai mạch giải mã 4 sang 16 bằng cách sử dụng mạch giải mã 3 sang 8. Chúng ta biết rằng mạch giải mã 3 sang 8 có ba đầu vào A2, A1 & A0 và tám đầu ra, Y7 đến Y0. Trong khi, mạch giải mã 4 sang 16 có bốn đầu vào A3, A2, A1 & A0 và mười sáu đầu ra, Y15 đến Y0

Chúng ta đã biết công thức sau để tìm số mạch giải mã bậc thấp hơn cần thiết ở trên.

Thay thế, m1 = 8 và m2 = 16 vào công thức ta có

m2/m1 = 2

Do đó, chúng ta cần 2 mạch giải mã từ 3 sang 8 để triển khai 1 mạch giải mã 4 sang 16. Sơ đồ khối của mạch giải mã 4 sang 16 sử dụng mạch giải mã 3 sang 8 được thể hiện trong hình sau.

Xem thêm: Giải Vbt Lịch Sử 8 Bài 3 – Bài Tập 3 Trang 8 Sách Bài Tập (Sbt) Lịch Sử 8

Các đầu vào song song A2, A1 & A0 được áp dụng cho mỗi mạch giải mã từ 3 sang 8. Phần bổ sung của đầu vào, A3 được kết nối với Enable, E của bộ giải mã thấp hơn từ 3 sang 8 để nhận các đầu ra, Y7 đến Y0. Đây là tám số hạng tối thiểu thấp hơn. Đầu vào, A3 được kết nối trực tiếp với Enable, E của bộ giải mã 3 sang 8 trên để nhận các đầu ra, Y15 đến Y8. Đây là tám số hạng tối thiểu cao hơn.

Cảm ơn bạn đã đọc bài viết Nguyên Lý Mạch Giải Mã . Đừng quên truy cập Chaolong TV kênh trực tiếp bóng đá số 1 Việt Nam hiện nay để có những phút giây thư giãn cùng trái bóng tròn !